JTAG and Boundary Scan are both techniques used for testing and debugging integrated circuits, with JTAG serving as the hardware interface standard while Boundary Scan focuses on accessing and controlling individual pins on a device. Your choice depends on whether you need comprehensive device programming and debug capabilities with JTAG or precise testing of interconnections and solder joints using Boundary Scan.

Table of Comparison

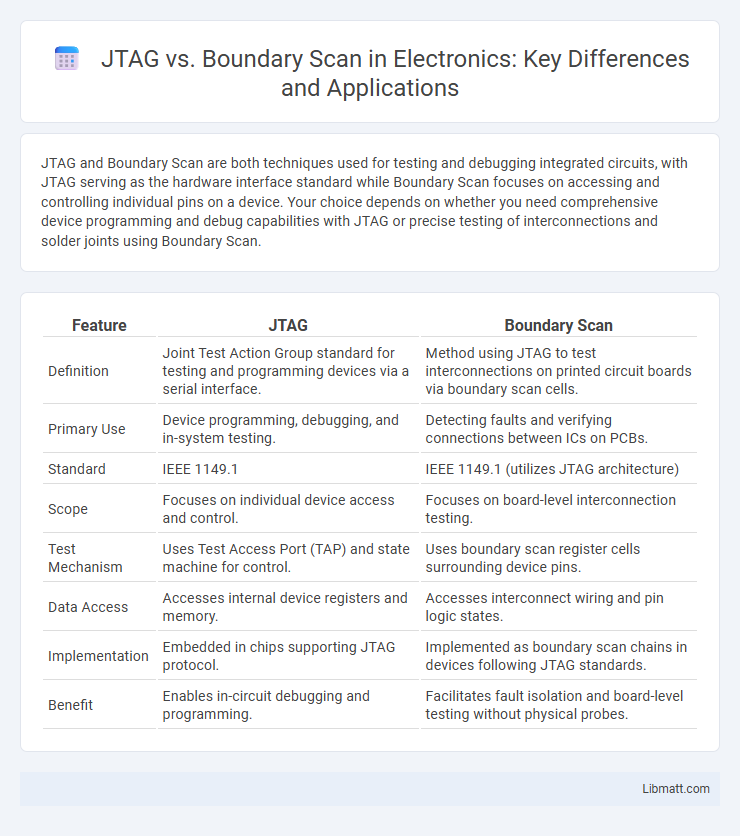

| Feature | JTAG | Boundary Scan |

|---|---|---|

| Definition | Joint Test Action Group standard for testing and programming devices via a serial interface. | Method using JTAG to test interconnections on printed circuit boards via boundary scan cells. |

| Primary Use | Device programming, debugging, and in-system testing. | Detecting faults and verifying connections between ICs on PCBs. |

| Standard | IEEE 1149.1 | IEEE 1149.1 (utilizes JTAG architecture) |

| Scope | Focuses on individual device access and control. | Focuses on board-level interconnection testing. |

| Test Mechanism | Uses Test Access Port (TAP) and state machine for control. | Uses boundary scan register cells surrounding device pins. |

| Data Access | Accesses internal device registers and memory. | Accesses interconnect wiring and pin logic states. |

| Implementation | Embedded in chips supporting JTAG protocol. | Implemented as boundary scan chains in devices following JTAG standards. |

| Benefit | Enables in-circuit debugging and programming. | Facilitates fault isolation and board-level testing without physical probes. |

Introduction to JTAG and Boundary Scan

JTAG (Joint Test Action Group) is a standardized interface used for testing and debugging integrated circuits through a serial communication protocol. Boundary Scan is a technique defined by the JTAG standard (IEEE 1149.1) that enables testing of interconnects on printed circuit boards without physical test probes. Both JTAG and Boundary Scan provide improved fault detection and streamline the validation process for complex electronic assemblies.

Overview of JTAG Technology

JTAG technology, formally known as IEEE 1149.1, is a standardized test access port and boundary scan architecture used for testing printed circuit boards and integrated circuits. It enables access to the test logic embedded within chips via a serial interface, facilitating tasks such as device programming, debugging, and fault detection without physical probing. This technology supports efficient verification and diagnosis by shifting test data through a chain of boundary scan cells surrounding the device's pins.

Understanding Boundary Scan Techniques

Boundary Scan is a standardized testing technique defined by IEEE 1149.1 that uses JTAG (Joint Test Action Group) protocols to access and control individual pins of integrated circuits for fault detection and debugging. Unlike traditional JTAG, which primarily facilitates device programming and debugging, Boundary Scan enables systematic testing of interconnects on printed circuit boards without physical probe access. This technique improves testing coverage, reduces production costs, and accelerates fault isolation by capturing data directly from the device's boundary-scan cells embedded in the chip's I/O pins.

Key Differences Between JTAG and Boundary Scan

JTAG (Joint Test Action Group) is a standard for verifying designs and testing printed circuit boards using a serial communication protocol, while Boundary Scan is a technique implemented through JTAG that allows testing of interconnects without physical probes. The key differences lie in their scope and application: JTAG defines the interface and communication protocol for testing, whereas Boundary Scan utilizes this interface to inspect and control the individual pins of integrated circuits. Your testing strategy benefits from understanding that JTAG is the foundation enabling Boundary Scan's detailed board-level diagnostics.

Use Cases in Electronics Testing

JTAG is widely used for programming, debugging, and verifying the functionality of integrated circuits at the chip level, making it essential for semiconductor manufacturing and development environments. Boundary Scan, a standardized extension of JTAG (IEEE 1149.1), facilitates testing of interconnections on printed circuit boards (PCBs) without physical test probes, enabling detection of soldering defects and open or short circuits. Both methods improve fault coverage and streamline production testing, with JTAG primarily focusing on internal device testing and Boundary Scan targeting system-level board testing.

Benefits of JTAG vs Boundary Scan

JTAG offers in-system programming and debugging capabilities that extend beyond the structural testing provided by Boundary Scan, enabling real-time fault diagnosis and system verification. Boundary Scan primarily facilitates interconnect testing and manufacturing defect detection, while JTAG encompasses a broader scope including processor control and firmware updates. Utilizing JTAG enhances your ability to perform comprehensive system validation and repair, thereby reducing downtime and improving product reliability.

Limitations and Challenges

JTAG faces limitations such as restricted pin availability and signal integrity issues in high-speed applications. Boundary Scan struggles with complexity when testing densely packed integrated circuits and may require specialized test equipment. Your ability to effectively diagnose hardware faults depends on understanding these challenges and selecting the appropriate method for your specific testing requirements.

Hardware and Software Requirements

JTAG (Joint Test Action Group) requires compliant hardware including a dedicated Test Access Port (TAP) with TCK, TMS, TDI, and TDO pins, alongside software tools capable of generating and interpreting test vectors for device programming and debugging. Boundary Scan builds on JTAG hardware but emphasizes specialized software support to implement boundary-scan description language (BSDL) files and execute tests on interconnects and pin states without physical probing. Effective use of both technologies demands integrated development environments (IDEs) that support IEEE 1149.1 standard protocols for seamless hardware control and test automation.

Industry Adoption and Standards

JTAG and Boundary Scan are widely adopted in the electronics industry for testing and debugging integrated circuits, with JTAG established as IEEE Standard 1149.1, ensuring interoperability across devices and vendors. Boundary Scan, an implementation of the JTAG standard, is incorporated in numerous industry sectors including aerospace, automotive, and telecommunications to facilitate fault detection and board-level testing without physical probes. Your choice between JTAG and Boundary Scan depends on adherence to these industry standards and the specific diagnostic needs of your embedded systems.

Choosing the Right Solution for Your Project

Selecting between JTAG and Boundary Scan depends on the specific testing and debugging requirements of your project. JTAG provides comprehensive access to internal chip registers for in-depth system diagnostics, while Boundary Scan focuses on testing PCB interconnections without physical probing. Evaluate your hardware complexity, test coverage needs, and development timeline to determine the optimal approach for efficient fault isolation and enhanced production testing.

JTAG vs Boundary Scan Infographic

libmatt.com

libmatt.com