RISC architectures use a smaller set of simple instructions that can be executed rapidly, improving processor speed and efficiency for tasks requiring consistent performance. CISC designs focus on complex instructions that perform multiple operations in a single command, optimizing your system for tasks that benefit from more versatile and powerful instruction sets.

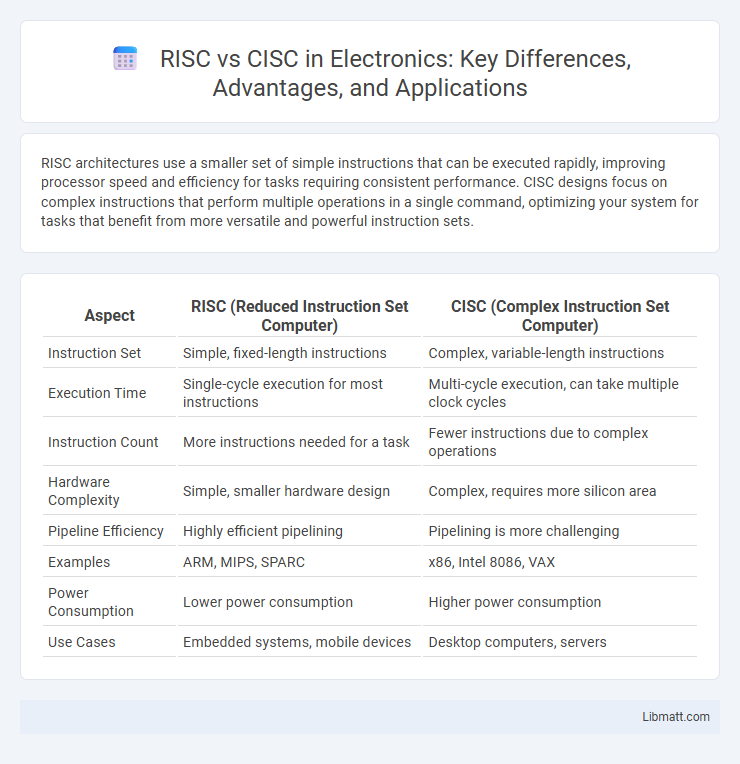

Table of Comparison

| Aspect | RISC (Reduced Instruction Set Computer) | CISC (Complex Instruction Set Computer) |

|---|---|---|

| Instruction Set | Simple, fixed-length instructions | Complex, variable-length instructions |

| Execution Time | Single-cycle execution for most instructions | Multi-cycle execution, can take multiple clock cycles |

| Instruction Count | More instructions needed for a task | Fewer instructions due to complex operations |

| Hardware Complexity | Simple, smaller hardware design | Complex, requires more silicon area |

| Pipeline Efficiency | Highly efficient pipelining | Pipelining is more challenging |

| Examples | ARM, MIPS, SPARC | x86, Intel 8086, VAX |

| Power Consumption | Lower power consumption | Higher power consumption |

| Use Cases | Embedded systems, mobile devices | Desktop computers, servers |

Introduction to RISC and CISC Architectures

RISC (Reduced Instruction Set Computer) architecture streamlines processing by using a small set of simple instructions, enabling faster execution and efficiency in modern computing devices. CISC (Complex Instruction Set Computer) architecture features a broader set of instructions designed to perform complex tasks in fewer lines of code, often found in legacy systems and desktop processors. Understanding these architectures helps you optimize software performance based on hardware capabilities.

Defining RISC: Key Features and Principles

RISC (Reduced Instruction Set Computer) architecture emphasizes a small, highly optimized set of instructions aimed at executing operations rapidly and efficiently. Key features include fixed-length instructions, load/store architecture separating memory access and computation, and a focus on pipelining to enhance instruction throughput. These principles enable simpler hardware design, which supports faster instruction execution and lower power consumption compared to complex instruction set computing (CISC).

Defining CISC: Core Characteristics and Concepts

CISC (Complex Instruction Set Computing) architecture features a rich set of instructions capable of executing multi-step operations within single instructions, reducing the number of instructions per program. Core characteristics include variable-length instructions, numerous addressing modes, and the ability to perform complex tasks like memory manipulation directly in hardware. This design aims to enhance performance by minimizing the instruction cycle count but can lead to increased CPU complexity and power consumption.

Historical Development of RISC and CISC

The historical development of RISC (Reduced Instruction Set Computing) began in the early 1980s as a response to the complexity and inefficiency of CISC (Complex Instruction Set Computing) architectures, which dominated the 1970s with their extensive instruction sets designed to perform complex tasks in a single instruction. RISC emphasized simplified instructions that could be executed rapidly, enabling higher performance through faster clock speeds and more efficient pipelining, influencing modern processors like ARM and MIPS. Your understanding of this evolution highlights how RISC's streamlined approach contrasts with CISC's intricate design, shaping the foundation of contemporary CPU architectures.

Instruction Set Design: Simplicity vs. Complexity

RISC (Reduced Instruction Set Computer) architectures emphasize a simplified instruction set with fixed-length instructions, enabling faster execution and easier pipelining. CISC (Complex Instruction Set Computer) designs incorporate variable-length, complex instructions that perform multiple operations, aiming to reduce the number of instructions per program. The simplicity of RISC enhances compiler optimization and energy efficiency, while CISC's complexity targets legacy software compatibility and reduced memory usage.

Performance Differences: Speed, Efficiency, and Processing

RISC architecture enhances performance by utilizing a simplified instruction set that executes operations in a single clock cycle, resulting in faster processing speeds and improved efficiency. CISC designs handle more complex instructions per cycle, but this can lead to slower execution and higher power consumption due to additional decoding stages. Your choice between RISC and CISC impacts system throughput, with RISC excelling in speed and efficiency for applications requiring rapid instruction execution.

Power Consumption and Energy Efficiency

RISC processors typically consume less power due to their simplified instruction sets and streamlined execution pipelines, which reduce the number of transistors switching at any given time. CISC architectures often require more complex decoding and execution stages, leading to higher power consumption and lower energy efficiency in comparison. Energy efficiency in RISC designs makes them ideal for battery-powered and embedded systems where power conservation is critical.

Programming Model and Compiler Support

RISC architectures feature a simplified programming model with a fixed instruction length and a limited set of instructions, which enables more straightforward and efficient compiler optimizations. CISC designs encompass a more complex instruction set with variable-length instructions and multiple addressing modes, posing greater challenges for compilers to generate optimized code. Your choice between RISC and CISC impacts compiler design and programming efficiency, as RISC often leads to faster compilation and simpler code generation.

Real-World Applications: Where RISC and CISC Excel

RISC processors excel in mobile devices, embedded systems, and applications requiring low power consumption and high efficiency due to their simplified instruction sets and faster execution cycles. CISC processors dominate desktop computing, servers, and legacy software environments where complex instructions and backward compatibility provide advantages in handling diverse and intensive tasks. Both architectures coexist with RISC preferred for energy-efficient performance and CISC favored for versatility and software compatibility in real-world applications.

Future Trends: The Evolution of Processor Architectures

Future trends in processor architectures emphasize increased integration of RISC (Reduced Instruction Set Computing) cores due to their power efficiency and scalability in AI and edge computing applications. CISC (Complex Instruction Set Computing) designs are evolving by adopting RISC principles, enhancing performance through hybrid approaches that combine simplicity with complex instruction sets. Your computing needs will benefit from advances in hybrid architectures that leverage the strengths of both RISC and CISC for optimized speed and energy consumption.

RISC vs CISC Infographic

libmatt.com

libmatt.com