Flip flop and latch are both fundamental memory elements in digital electronics, but flip flops are edge-triggered devices that change state only at specific clock edges, while latches are level-triggered and change state whenever the enable signal is active. Your choice depends on timing requirements: flip flops offer better synchronization in clocked systems, whereas latches can provide faster response times in asynchronous designs.

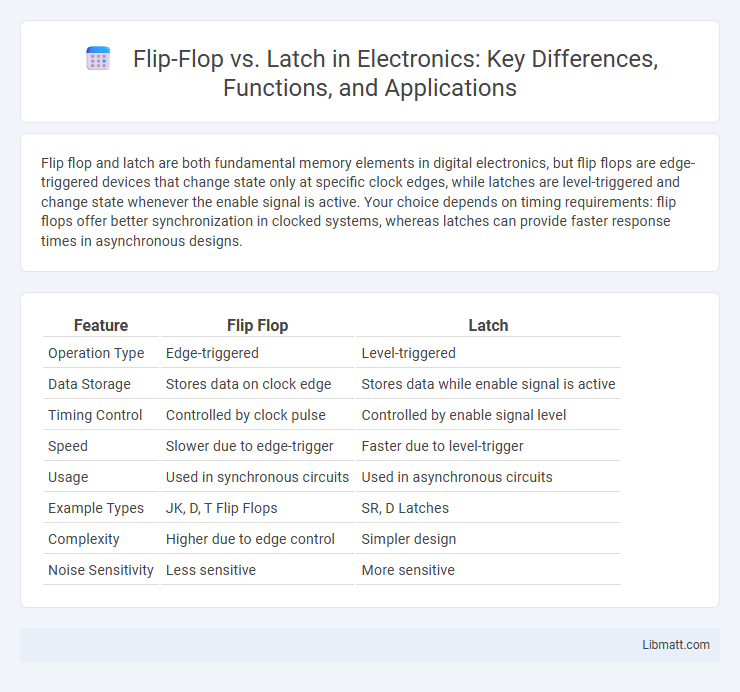

Table of Comparison

| Feature | Flip Flop | Latch |

|---|---|---|

| Operation Type | Edge-triggered | Level-triggered |

| Data Storage | Stores data on clock edge | Stores data while enable signal is active |

| Timing Control | Controlled by clock pulse | Controlled by enable signal level |

| Speed | Slower due to edge-trigger | Faster due to level-trigger |

| Usage | Used in synchronous circuits | Used in asynchronous circuits |

| Example Types | JK, D, T Flip Flops | SR, D Latches |

| Complexity | Higher due to edge control | Simpler design |

| Noise Sensitivity | Less sensitive | More sensitive |

Introduction to Flip Flops and Latches

Flip flops and latches are fundamental building blocks in digital electronics used for storing binary information. Flip flops operate on clock edges, making them edge-triggered devices, while latches are level-sensitive, responding to input signals as long as the enable signal is active. Both are essential for designing sequential circuits, with flip flops commonly used in synchronous systems and latches in asynchronous or simpler memory tasks.

Fundamental Definitions

A flip flop is a bistable multivibrator used in digital circuits to store binary data, triggered by clock edges, ensuring synchronization with system timing. A latch is a level-sensitive device that holds data as long as its enable signal is active, making it more susceptible to glitches compared to flip flops. Both components are essential for memory elements in sequential logic, with flip flops offering edge-triggered stability and latches providing simpler, faster data storage.

Core Differences Between Flip Flops and Latches

Flip flops and latches are fundamental memory elements in digital circuits, differing primarily in their timing control: flip flops are edge-triggered devices that change state only at specific clock edges, ensuring synchronized data storage, whereas latches are level-sensitive and can change state whenever the control signal is active. Flip flops provide greater stability and are widely used in synchronous systems, while latches offer simpler designs but risk data transparency issues during input signal changes. Understanding these core differences helps you choose the right component for precise timing and data integrity in sequential logic designs.

Working Principles Explained

Flip flops and latches are fundamental memory elements used in digital circuits, operating based on bistable multivibrator principles. Latches function as level-triggered devices, meaning they change output state when the enable signal is active, storing data as long as the enable signal is high. Flip flops, being edge-triggered, capture and store input data precisely on the clock signal's rising or falling edge, ensuring synchronized data transfer in sequential logic circuits.

Types of Flip Flops and Latches

Flip flops include types such as SR, D, JK, and T, each serving different functions in digital circuits by storing binary data with edge-triggered inputs. Latches, primarily categorized as SR and D types, operate based on level-triggered inputs and hold data while the enable signal is active. Differences in timing control between flip flops and latches impact their use in synchronous versus asynchronous circuit designs.

Timing and Triggering Mechanisms

Flip flops operate based on edge-triggering, capturing input data only at specific clock edges, ensuring precise timing control in synchronous circuits. Latches are level-triggered devices that continuously monitor inputs while the enable signal is active, which can lead to potential timing hazards in design. The timing mechanism in flip flops offers better noise immunity and timing predictability compared to latches, making them ideal for clocked sequential logic.

Applications in Digital Circuits

Flip flops are essential in digital circuits for synchronous data storage, edge-triggered operations, and timing applications like counters and shift registers. Latches serve well in asynchronous circuits where level-sensitive data storage and temporary holding of signals are required, such as in transparent data latches and buffering. Your choice between flip flop and latch depends on the need for precise timing control or simple data holding within digital systems.

Advantages and Disadvantages

Flip flops offer edge-triggered control, ensuring data changes only at clock edges, which reduces timing errors and enhances synchronization in digital circuits. Latches provide level-sensitive operation, allowing faster data capture but risk data instability if inputs change during the active level. Your choice depends on speed requirements and timing stability, with flip flops favored for precise timing and latches for simpler, lower-latency designs.

Comparison Table: Flip Flop vs Latch

Flip Flops and Latches differ primarily in their timing control: Flip Flops are edge-triggered devices capturing input only at clock signal transitions, while Latches are level-sensitive and respond continuously as long as the enable signal is active. Flip Flops provide better data stability and synchronization in digital circuits, whereas Latches offer faster operation with simpler design but risk glitches due to their transparency during enable. Your choice between these components depends on the required timing precision and circuit complexity, as summarized in the comparison table highlighting triggering mechanism, speed, complexity, and application suitability.

Conclusion and Final Insights

Flip flops and latches both serve as essential bistable storage elements in digital circuits, with flip flops triggered by clock edges providing precise timing control ideal for synchronous designs. Latches are level-sensitive devices offering simpler implementation but risk timing hazards in asynchronous environments. Selecting between them hinges on design requirements for timing accuracy, complexity, power consumption, and susceptibility to glitches.

Flip Flop vs Latch Infographic

libmatt.com

libmatt.com