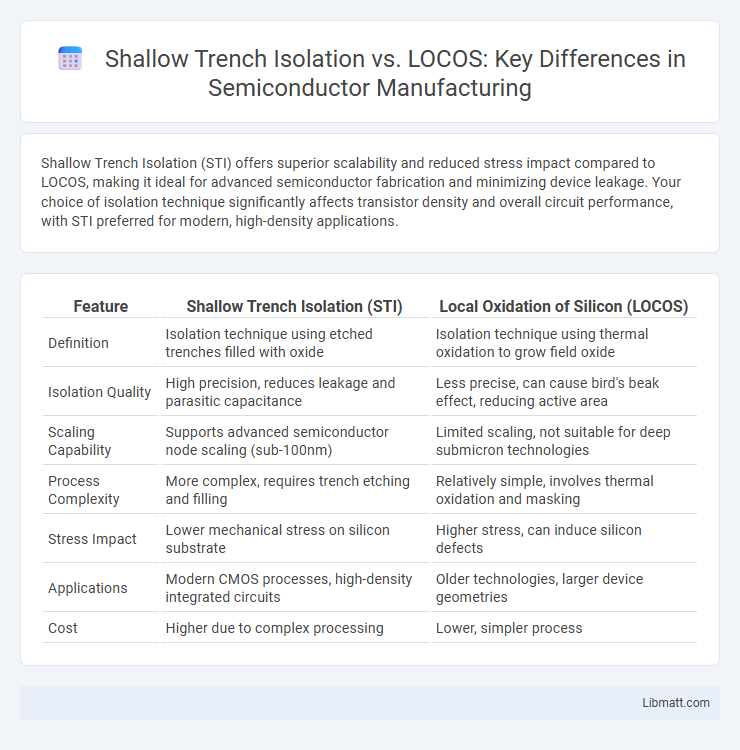

Shallow Trench Isolation (STI) offers superior scalability and reduced stress impact compared to LOCOS, making it ideal for advanced semiconductor fabrication and minimizing device leakage. Your choice of isolation technique significantly affects transistor density and overall circuit performance, with STI preferred for modern, high-density applications.

Table of Comparison

| Feature | Shallow Trench Isolation (STI) | Local Oxidation of Silicon (LOCOS) |

|---|---|---|

| Definition | Isolation technique using etched trenches filled with oxide | Isolation technique using thermal oxidation to grow field oxide |

| Isolation Quality | High precision, reduces leakage and parasitic capacitance | Less precise, can cause bird's beak effect, reducing active area |

| Scaling Capability | Supports advanced semiconductor node scaling (sub-100nm) | Limited scaling, not suitable for deep submicron technologies |

| Process Complexity | More complex, requires trench etching and filling | Relatively simple, involves thermal oxidation and masking |

| Stress Impact | Lower mechanical stress on silicon substrate | Higher stress, can induce silicon defects |

| Applications | Modern CMOS processes, high-density integrated circuits | Older technologies, larger device geometries |

| Cost | Higher due to complex processing | Lower, simpler process |

Introduction to Isolation Techniques in Semiconductor Manufacturing

Shallow Trench Isolation (STI) and Local Oxidation of Silicon (LOCOS) are critical semiconductor isolation techniques used to electrically separate devices on a silicon wafer. STI involves etching shallow trenches filled with dielectric material, providing superior planarization and reduced device spacing, while LOCOS grows thick oxide regions through localized oxidation but suffers from bird's beak encroachment. Understanding these methods enables you to optimize isolation in integrated circuits, balancing device density, performance, and manufacturing complexity.

Overview of Shallow Trench Isolation (STI)

Shallow Trench Isolation (STI) offers a precise method for electrically isolating active regions in integrated circuits using narrow trenches filled with dielectric materials. Unlike LOCOS (Local Oxidation of Silicon), STI enables higher device density and better planarization without the bird's beak effect, making it ideal for advanced CMOS technology nodes. Your semiconductor designs benefit from STI by achieving improved scalability, reduced parasitic capacitance, and enhanced performance in modern microelectronics.

Fundamentals of LOCOS (Local Oxidation of Silicon)

LOCOS (Local Oxidation of Silicon) is a semiconductor fabrication process that creates field isolation by growing a silicon dioxide layer selectively on the silicon substrate through thermal oxidation. This method forms an isolation oxide region by patterning a silicon nitride mask, preventing oxidation where circuit elements are located, allowing you to electrically separate devices on a chip. LOCOS fundamentals involve controlling oxide thickness and stress management to minimize lateral encroachment, known as the "bird's beak" effect, which impacts device density.

Key Differences Between STI and LOCOS

Shallow Trench Isolation (STI) offers superior planarization and smaller isolation widths compared to Local Oxidation of Silicon (LOCOS), enabling higher device density in modern semiconductor fabrication. STI uses etched trenches filled with dielectric material, providing precise control over isolation dimensions, while LOCOS relies on thermal oxidation, which creates bird's beak structures that limit scaling. The reduced lateral oxidation in STI significantly improves scaling and reduces short-channel effects, making it the preferred choice for advanced CMOS technologies.

Process Steps: STI vs. LOCOS

Shallow Trench Isolation (STI) involves etching narrow trenches into the silicon substrate, followed by filling these trenches with a dielectric material such as silicon dioxide, and then performing a chemical-mechanical polishing (CMP) to planarize the surface. In contrast, Local Oxidation of Silicon (LOCOS) utilizes a thermal oxidation process where an oxide layer grows selectively on silicon regions, guided by a patterned nitride mask, creating isolation by forming field oxide areas around active devices. STI offers finer isolation features with better scalability compared to LOCOS, which typically produces larger encroachment known as bird's beak effects.

Advantages of Shallow Trench Isolation

Shallow Trench Isolation (STI) offers superior planarization and reduced lateral encroachment compared to LOCOS, enabling tighter device packing and improved yield for advanced semiconductor nodes. STI's precise etching process minimizes bird's beak formation, leading to enhanced scaling and better device isolation. This technique supports higher integration density and improved electrical characteristics by decreasing parasitic capacitance and leakage currents.

Limitations of Shallow Trench Isolation

Shallow Trench Isolation (STI) faces limitations such as increased process complexity and potential stress-induced defects in the silicon substrate, which can degrade device performance. Compared to LOCOS, STI requires precise etching and fill processes that may introduce dishing and trench-topography variations affecting transistor electrical characteristics. Furthermore, STI's scaling challenges arise from difficulties in maintaining isolation effectiveness as device dimensions shrink below the sub-100 nm technology node.

Benefits and Drawbacks of LOCOS

LOCOS (Local Oxidation of Silicon) offers benefits such as excellent isolation quality and low defect density, making it suitable for analog and high-voltage devices. However, LOCOS suffers from drawbacks including bird's beak formation, which reduces effective device area and limits scaling for advanced technologies. Your choice of isolation technique depends on balancing LOCOS's robustness against the miniaturization challenges faced in modern semiconductor fabrication.

Application Suitability: STI vs. LOCOS

Shallow Trench Isolation (STI) is highly suitable for advanced CMOS technologies due to its precise trench etching and filling process, enabling tighter device packing and reduced parasitic capacitance. LOCOS, or Local Oxidation of Silicon, is better suited for older, larger-geometry technologies where simplicity and lower process complexity are prioritized despite larger isolation areas and bird's beak formation. Your choice between STI and LOCOS should consider device scaling requirements and the need for isolation precision in modern integrated circuits.

Future Trends in Isolation Technology

Shallow Trench Isolation (STI) is rapidly becoming the preferred method over LOCOS due to its superior scalability and reduced device stress in advanced semiconductor nodes below 10nm. Future trends emphasize further miniaturization with STI, enhanced dielectric materials, and integration of novel processes like plasma doping to improve isolation performance. Emerging technologies also explore combining STI with high-k dielectrics for better leakage control and compatibility with 3D transistor architectures.

Shallow Trench Isolation vs LOCOS Infographic

libmatt.com

libmatt.com