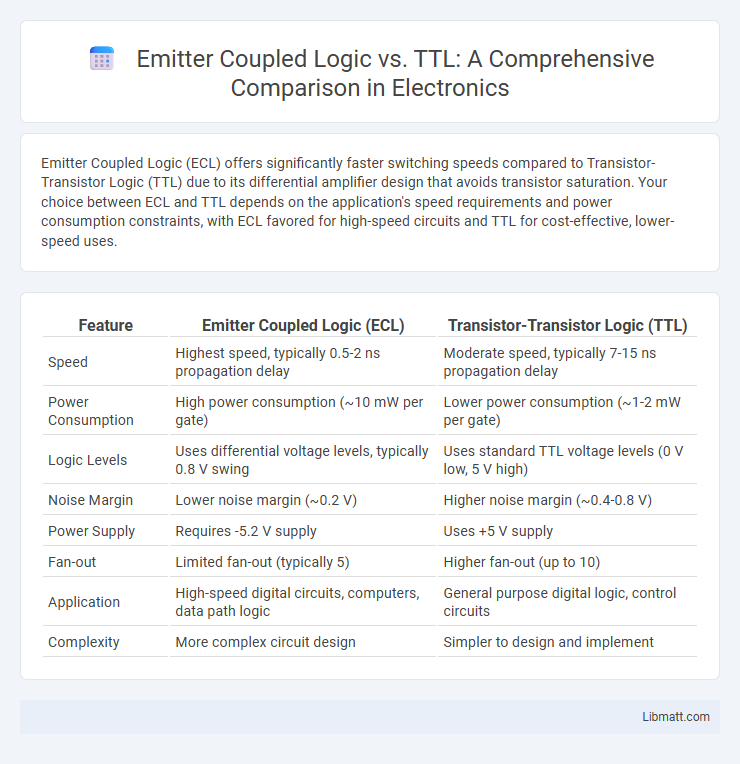

Emitter Coupled Logic (ECL) offers significantly faster switching speeds compared to Transistor-Transistor Logic (TTL) due to its differential amplifier design that avoids transistor saturation. Your choice between ECL and TTL depends on the application's speed requirements and power consumption constraints, with ECL favored for high-speed circuits and TTL for cost-effective, lower-speed uses.

Table of Comparison

| Feature | Emitter Coupled Logic (ECL) | Transistor-Transistor Logic (TTL) |

|---|---|---|

| Speed | Highest speed, typically 0.5-2 ns propagation delay | Moderate speed, typically 7-15 ns propagation delay |

| Power Consumption | High power consumption (~10 mW per gate) | Lower power consumption (~1-2 mW per gate) |

| Logic Levels | Uses differential voltage levels, typically 0.8 V swing | Uses standard TTL voltage levels (0 V low, 5 V high) |

| Noise Margin | Lower noise margin (~0.2 V) | Higher noise margin (~0.4-0.8 V) |

| Power Supply | Requires -5.2 V supply | Uses +5 V supply |

| Fan-out | Limited fan-out (typically 5) | Higher fan-out (up to 10) |

| Application | High-speed digital circuits, computers, data path logic | General purpose digital logic, control circuits |

| Complexity | More complex circuit design | Simpler to design and implement |

Introduction to Emitter Coupled Logic and TTL

Emitter Coupled Logic (ECL) is a high-speed digital logic family known for its low propagation delay and high-frequency operation, using differential amplifier stages and constant current sources. Transistor-Transistor Logic (TTL) relies on bipolar junction transistors to perform logic functions with moderate speed and power consumption, commonly used in early digital circuits. ECL outperforms TTL in speed due to its non-saturating transistor operation, making it suitable for high-frequency applications despite higher power dissipation.

Overview of ECL and TTL Architectures

Emitter Coupled Logic (ECL) architecture utilizes differential amplifier stages to achieve high-speed switching with minimal voltage swing, resulting in faster operation and reduced signal delay compared to Transistor-Transistor Logic (TTL). TTL architecture relies on multiple bipolar junction transistors configured in multi-emitter input stages and totem-pole output stages, prioritizing simplicity and ease of integration but with slower switching speeds than ECL. ECL's constant current biasing contrasts with TTL's saturation mode switching, providing superior speed at the cost of higher power consumption.

Key Differences in Circuit Design

Emitter Coupled Logic (ECL) utilizes differential amplifier transistor pairs operating in the active region, enabling high-speed switching with minimal voltage swing, whereas Transistor-Transistor Logic (TTL) relies on multiple transistor stages with saturated switching, resulting in slower transition times. ECL circuits maintain constant current flow, reducing noise and propagation delay, while TTL circuits exhibit larger voltage swings and slower rise/fall times due to charge storage effects in saturated transistors. The current-steering architecture of ECL allows for faster, more stable operation at the cost of higher power consumption compared to the simpler, lower-power TTL design.

Speed Comparison: ECL vs TTL

Emitter Coupled Logic (ECL) offers significantly higher switching speeds than Transistor-Transistor Logic (TTL), with propagation delays in the range of picoseconds to low nanoseconds compared to several nanoseconds typical for TTL. ECL's high-speed advantage is due to its differential amplifier configuration and the absence of transistor saturation, enabling faster transistor switching. Despite higher power consumption, ECL is preferred in applications requiring ultra-fast logic performance such as high-frequency telecommunications and supercomputing.

Power Consumption Analysis

Emitter Coupled Logic (ECL) exhibits significantly lower propagation delay compared to TTL but consumes higher power due to its constant current operation, even when not switching. TTL circuits, in contrast, draw power primarily during state transitions, resulting in generally lower overall power consumption for typical digital logic tasks. Your choice should consider that ECL's superior speed comes at the cost of greater power dissipation, making TTL more suitable for power-sensitive applications.

Noise Immunity and Signal Integrity

Emitter Coupled Logic (ECL) offers superior noise immunity compared to Transistor-Transistor Logic (TTL) due to its differential signaling and constant current operation, which minimizes voltage fluctuations and signal distortion. ECL's fast switching speeds maintain signal integrity even at high frequencies, reducing timing errors and propagation delays commonly seen in TTL circuits. TTL circuits, while simpler and more cost-effective, are more susceptible to noise and signal degradation under high-speed and high-density conditions.

Application Domains for ECL and TTL

Emitter Coupled Logic (ECL) excels in high-speed applications such as supercomputers, military radar systems, and high-frequency telecommunications due to its fast switching capabilities. Transistor-Transistor Logic (TTL) is widely used in general-purpose digital circuits, microcontrollers, and consumer electronics where low power consumption and cost-effectiveness are important. Your choice between ECL and TTL depends on whether speed or energy efficiency and affordability are prioritized in the specific application domain.

Cost Considerations

Emitter Coupled Logic (ECL) circuits typically incur higher costs compared to Transistor-Transistor Logic (TTL) due to their complex design and faster switching speeds demanding more sophisticated fabrication processes. TTL components offer a cost-effective solution for applications where speed is less critical, benefiting from widespread manufacturing and mature technology. Your choice between ECL and TTL should weigh the budget constraints against performance requirements, as ECL's premium cost delivers superior speed but at increased expense.

Compatibility and Interfacing Challenges

Emitter Coupled Logic (ECL) operates at significantly higher speeds but uses lower voltage swings compared to Transistor-Transistor Logic (TTL), leading to compatibility challenges in interfacing the two logic families. Voltage level mismatches require careful design of translation circuits or level shifters to prevent signal integrity issues and ensure reliable communication between ECL and TTL devices. Furthermore, differing input/output impedances and power supply requirements necessitate attention to buffering, timing synchronization, and noise margins when integrating ECL and TTL components.

Future Trends in Digital Logic Families

Emitter Coupled Logic (ECL) offers significantly higher speed compared to Transistor-Transistor Logic (TTL), making it suitable for ultra-high-frequency applications in digital circuits. Future trends indicate a shift towards Low-Voltage Differential Signaling (LVDS) and integrated Silicon-Germanium (SiGe) BiCMOS technologies that combine the speed of ECL with the power efficiency and integration density close to CMOS. The evolution of digital logic families will emphasize reduced power consumption, higher switching speeds, and improved noise immunity, with ECL-inspired designs influencing high-performance computing and telecommunications infrastructure.

Emitter Coupled Logic vs TTL Infographic

libmatt.com

libmatt.com