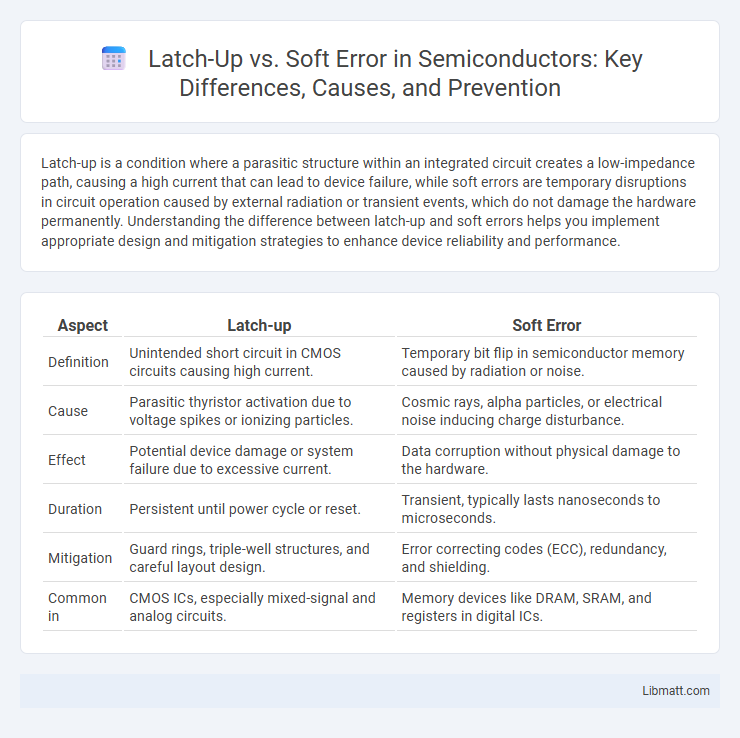

Latch-up is a condition where a parasitic structure within an integrated circuit creates a low-impedance path, causing a high current that can lead to device failure, while soft errors are temporary disruptions in circuit operation caused by external radiation or transient events, which do not damage the hardware permanently. Understanding the difference between latch-up and soft errors helps you implement appropriate design and mitigation strategies to enhance device reliability and performance.

Table of Comparison

| Aspect | Latch-up | Soft Error |

|---|---|---|

| Definition | Unintended short circuit in CMOS circuits causing high current. | Temporary bit flip in semiconductor memory caused by radiation or noise. |

| Cause | Parasitic thyristor activation due to voltage spikes or ionizing particles. | Cosmic rays, alpha particles, or electrical noise inducing charge disturbance. |

| Effect | Potential device damage or system failure due to excessive current. | Data corruption without physical damage to the hardware. |

| Duration | Persistent until power cycle or reset. | Transient, typically lasts nanoseconds to microseconds. |

| Mitigation | Guard rings, triple-well structures, and careful layout design. | Error correcting codes (ECC), redundancy, and shielding. |

| Common in | CMOS ICs, especially mixed-signal and analog circuits. | Memory devices like DRAM, SRAM, and registers in digital ICs. |

Introduction to Latch-up and Soft Error

Latch-up is a failure mechanism in CMOS devices caused by the inadvertent creation of a low-impedance path between power and ground, leading to device malfunction or permanent damage. Soft errors are transient faults in semiconductor devices induced by external radiation particles, resulting in temporary data corruption without physical harm to the hardware. Both phenomena affect integrated circuit reliability but differ fundamentally in cause, permanence, and recovery methods.

Definition of Latch-up

Latch-up is a short circuit condition in integrated circuits where parasitic components create a low-impedance path between power and ground, causing high current flow that can lead to device failure. Unlike soft errors, which are transient faults caused by external radiation or environmental noise, latch-up is a permanent fault requiring power cycling or may cause permanent damage. Understanding latch-up is crucial for designing robust semiconductor devices that prevent unintended triggering of these destructive conduction paths.

Definition of Soft Error

Soft error is a transient fault in semiconductor devices caused by external radiation or alpha particles that alters the stored data without causing permanent damage. Unlike latch-up, which creates a persistent short circuit and can destroy the device, soft errors temporarily disrupt your system's data integrity but do not affect hardware functionality. Understanding soft error helps improve error correction techniques and enhance system reliability.

Causes of Latch-up in Circuits

Latch-up in circuits is primarily caused by parasitic thyristor structures formed within CMOS technology, which create a low-impedance path between power and ground when triggered by factors such as high voltage spikes, ionizing radiation, or sudden changes in current. This condition leads to excessive current flow that can permanently damage the device if not interrupted. Ensuring proper layout techniques and guard rings can help mitigate latch-up risks in your circuit designs.

Causes of Soft Error in Electronics

Soft errors in electronics primarily result from energetic particles such as alpha particles and neutrons striking semiconductor devices, causing transient disruptions in circuit states. Cosmic rays at high altitudes and radioactive impurities within packaging materials contribute significantly to soft error rates. Device scaling and reduced node capacitance increase vulnerability to these ionizing particles, leading to bit flips and data corruption without permanent hardware damage.

Key Differences Between Latch-up and Soft Error

Latch-up is a short-circuit condition caused by parasitic structures in CMOS circuits leading to high current and potential device damage, while soft errors result from transient disturbances such as radiation-induced bit flips that do not cause permanent damage. The key difference lies in latch-up's persistent state requiring power cycling to clear, contrasting with soft errors' temporary data corruption corrected by error detection and correction mechanisms. Understanding these distinctions helps optimize your circuit design for reliability in harsh environments.

Effects of Latch-up on Device Performance

Latch-up induces a high current state causing significant power consumption and potential permanent damage to CMOS devices. This phenomenon leads to device malfunction, increased thermal stress, and degradation of circuit reliability. Recovery often requires power cycling, disrupting normal operation and reducing overall system performance.

Impact of Soft Error on System Reliability

Soft errors, caused by transient radiation events like cosmic rays or alpha particles, can alter data without physical damage, leading to data corruption and system malfunctions. Unlike latch-up, which results in a high current state potentially damaging hardware, soft errors primarily affect memory cells and logic states, reducing overall system reliability by causing unexpected crashes or erroneous outputs. Understanding the impact of soft errors is crucial for improving error detection and correction mechanisms in your system's design for enhanced reliability.

Prevention and Mitigation Techniques

Latch-up prevention involves using silicon-on-insulator (SOI) technology, guard rings, and well contacts to isolate parasitic structures and reduce current injection, minimizing the risk of device failure. Soft error mitigation relies on error-correcting code (ECC) memory, redundancy designs such as triple modular redundancy (TMR), and radiation-hardened circuits to detect and correct transient faults caused by charged particles. Your system's reliability improves significantly by integrating these tailored techniques to address latch-up susceptibility and soft error vulnerability in semiconductor devices.

Summary: Latch-up vs Soft Error

Latch-up is a hardware failure mode in CMOS circuits caused by parasitic thyristor activation, leading to high current flow and potential device damage. Soft errors result from transient disturbances, like cosmic rays or radiation, causing temporary data corruption without permanent hardware damage. Both phenomena impact system reliability but differ in their causes, effects, and recovery mechanisms.

Latch-up vs Soft Error Infographic

libmatt.com

libmatt.com