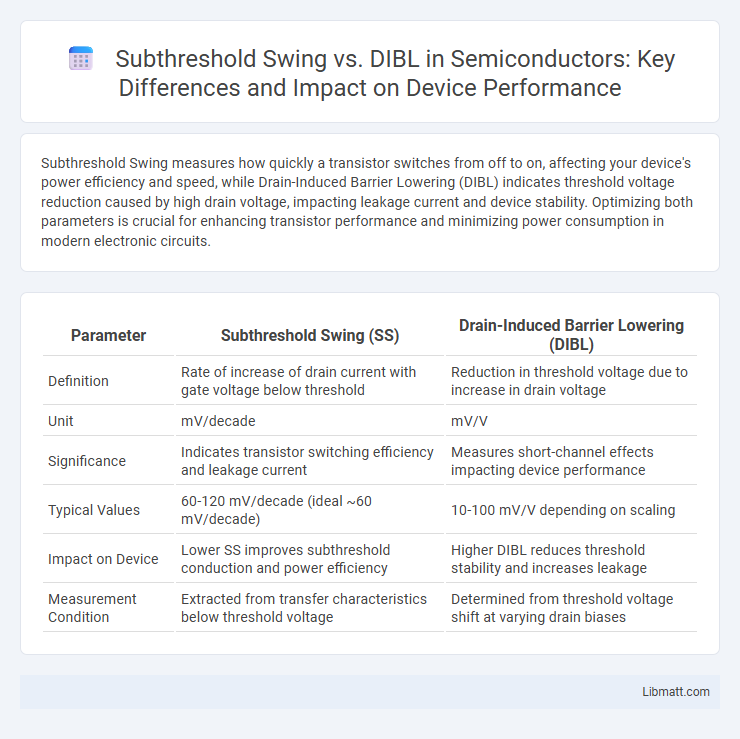

Subthreshold Swing measures how quickly a transistor switches from off to on, affecting your device's power efficiency and speed, while Drain-Induced Barrier Lowering (DIBL) indicates threshold voltage reduction caused by high drain voltage, impacting leakage current and device stability. Optimizing both parameters is crucial for enhancing transistor performance and minimizing power consumption in modern electronic circuits.

Table of Comparison

| Parameter | Subthreshold Swing (SS) | Drain-Induced Barrier Lowering (DIBL) |

|---|---|---|

| Definition | Rate of increase of drain current with gate voltage below threshold | Reduction in threshold voltage due to increase in drain voltage |

| Unit | mV/decade | mV/V |

| Significance | Indicates transistor switching efficiency and leakage current | Measures short-channel effects impacting device performance |

| Typical Values | 60-120 mV/decade (ideal ~60 mV/decade) | 10-100 mV/V depending on scaling |

| Impact on Device | Lower SS improves subthreshold conduction and power efficiency | Higher DIBL reduces threshold stability and increases leakage |

| Measurement Condition | Extracted from transfer characteristics below threshold voltage | Determined from threshold voltage shift at varying drain biases |

Introduction to Subthreshold Swing and DIBL

Subthreshold Swing (SS) quantifies the gate voltage required to change the drain current by one decade in a MOSFET, reflecting the device's switching efficiency and subthreshold leakage behavior. Drain-Induced Barrier Lowering (DIBL) measures the reduction in the threshold voltage caused by a high drain voltage, leading to increased off-state leakage and degraded device control. Both SS and DIBL are critical short-channel effects affecting transistor performance and power consumption in nanoscale semiconductor technologies.

Defining Subthreshold Swing in MOSFETs

Subthreshold Swing (SS) in MOSFETs measures the gate voltage required to increase the drain current by one order of magnitude in the subthreshold region, indicating the device's switching efficiency. Lower SS values signify better control of the channel by the gate voltage, leading to reduced power consumption and improved transistor performance. Understanding SS alongside Drain-Induced Barrier Lowering (DIBL) helps optimize your MOSFETs for faster switching and minimized leakage currents.

What is Drain Induced Barrier Lowering (DIBL)?

Drain Induced Barrier Lowering (DIBL) is a short-channel effect in MOSFETs where the threshold voltage decreases as the drain voltage increases, leading to reduced control of the gate over the channel barrier. This phenomenon occurs due to the lowering of the potential barrier at the source-channel junction caused by a high drain bias, resulting in increased leakage current and degraded device performance. DIBL is critical in nanoscale transistors, impacting subthreshold swing and overall device scalability by causing off-state current to rise.

Fundamental Differences Between Subthreshold Swing and DIBL

Subthreshold Swing (SS) measures how efficiently a transistor switches from off to on by quantifying the gate voltage change needed to increase the drain current by one decade, typically expressed in mV/decade. Drain-Induced Barrier Lowering (DIBL) quantifies the reduction in the threshold voltage as the drain voltage increases, indicating the influence of drain bias on the channel barrier height. The fundamental difference lies in SS focusing on the transistor's gate control over the channel at low currents, while DIBL reflects short-channel effects and the drain's impact on threshold voltage stability under high drain bias conditions.

Physical Mechanisms Behind Subthreshold Swing

Subthreshold Swing (SS) is primarily influenced by the thermionic emission of carriers over the potential barrier and the capacitive coupling between the gate and the channel, dictating how effectively the device switches off. Short-channel effects cause Drain-Induced Barrier Lowering (DIBL), reducing the effective barrier height and altering threshold voltage, thereby impacting the subthreshold behavior. The interplay between channel control, oxide capacitance, and depletion capacitance fundamentally governs the physical mechanisms behind the subthreshold swing in advanced MOSFETs.

Causes and Impacts of DIBL in Modern Transistors

Drain-Induced Barrier Lowering (DIBL) occurs in modern transistors when a high drain voltage reduces the potential barrier at the source-channel junction, causing premature leakage current and degraded device threshold voltage. This phenomenon directly impacts the subthreshold swing by increasing the off-state current, leading to higher power consumption and reduced switching efficiency in nanoscale transistors. Understanding DIBL is crucial for optimizing your transistor design to maintain sharp subthreshold slopes and ensure reliable low-power operation in advanced semiconductor technologies.

Subthreshold Swing vs DIBL: Effects on Device Performance

Subthreshold Swing (SS) measures the gate voltage needed to increase the drain current by one decade, critically impacting a transistor's switching speed and power efficiency. Drain-Induced Barrier Lowering (DIBL) quantifies the reduction in threshold voltage caused by drain voltage, leading to increased leakage currents and degraded device reliability. Optimizing Your device involves balancing low Subthreshold Swing for sharp switching with minimal DIBL to maintain threshold voltage stability and ensure robust performance.

Methods to Minimize Subthreshold Swing and DIBL

Minimizing subthreshold swing (SS) and drain-induced barrier lowering (DIBL) involves optimizing transistor design through techniques such as using high-k dielectrics and ultra-thin body channels to enhance gate control and reduce short-channel effects. Incorporating multi-gate structures like FinFETs or gate-all-around (GAA) transistors significantly improves electrostatic control, thereby lowering SS and DIBL simultaneously. Your device performance benefits from these methods by achieving better switching efficiency and reduced leakage currents in nanoscale MOSFETs.

Role in Scaling: Challenges at Nanoscale Dimensions

Subthreshold swing (SS) and drain-induced barrier lowering (DIBL) critically impact transistor scaling at nanoscale dimensions by affecting device control and leakage currents. SS determines how effectively a transistor can switch off, with lower SS enabling better gate control and reduced power consumption, while increased DIBL leads to threshold voltage reduction and degraded short-channel effects. Your ability to optimize these parameters is essential for maintaining performance and power efficiency in advanced semiconductor technologies as device dimensions approach the atomic scale.

Future Trends and Innovations in Subthreshold Swing and DIBL Control

Emerging technologies in semiconductor design are targeting ultra-low subthreshold swing to minimize power consumption and enhance energy efficiency in next-generation transistors. Advances in material engineering, such as the integration of 2D materials and novel high-k dielectrics, demonstrate significant promise in controlling Drain-Induced Barrier Lowering (DIBL) and improving device scalability. Your ability to leverage these innovations will be crucial in achieving superior transistor performance for future low-power applications.

Subthreshold Swing vs DIBL Infographic

libmatt.com

libmatt.com