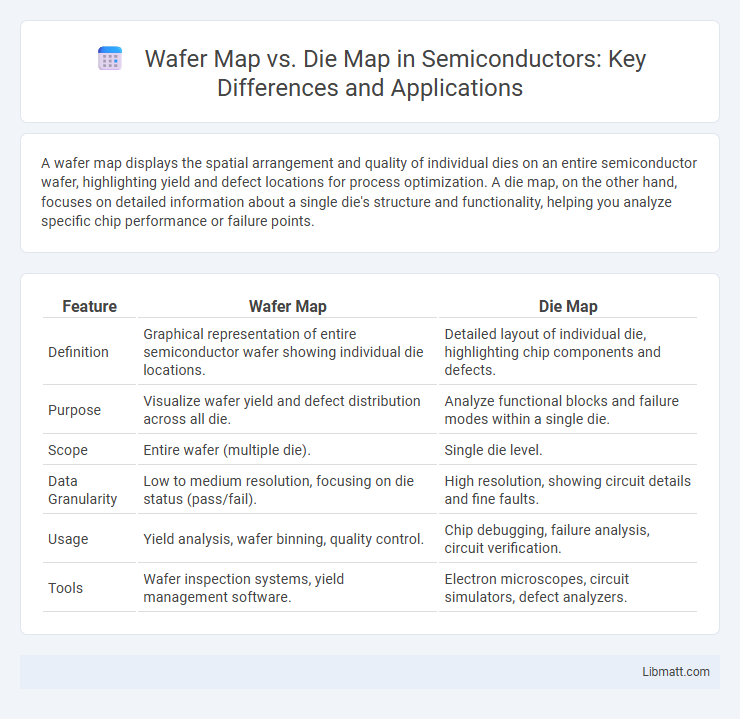

A wafer map displays the spatial arrangement and quality of individual dies on an entire semiconductor wafer, highlighting yield and defect locations for process optimization. A die map, on the other hand, focuses on detailed information about a single die's structure and functionality, helping you analyze specific chip performance or failure points.

Table of Comparison

| Feature | Wafer Map | Die Map |

|---|---|---|

| Definition | Graphical representation of entire semiconductor wafer showing individual die locations. | Detailed layout of individual die, highlighting chip components and defects. |

| Purpose | Visualize wafer yield and defect distribution across all die. | Analyze functional blocks and failure modes within a single die. |

| Scope | Entire wafer (multiple die). | Single die level. |

| Data Granularity | Low to medium resolution, focusing on die status (pass/fail). | High resolution, showing circuit details and fine faults. |

| Usage | Yield analysis, wafer binning, quality control. | Chip debugging, failure analysis, circuit verification. |

| Tools | Wafer inspection systems, yield management software. | Electron microscopes, circuit simulators, defect analyzers. |

Introduction to Wafer Maps and Die Maps

Wafer maps display the spatial distribution of dies on a semiconductor wafer, highlighting pass/fail results and process variations to analyze wafer quality. Die maps provide detailed information about individual die characteristics, often used for in-depth failure analysis and yield improvement. Understanding the differences between wafer maps and die maps empowers your semiconductor manufacturing process by enabling precise defect localization and performance assessment.

Defining Wafer Maps: Purpose and Functionality

Wafer maps visually represent the spatial distribution of semiconductor die performance on a wafer, identifying defect locations, yield, and quality variations. They serve as critical tools for process engineers to analyze manufacturing defects and optimize wafer fabrication. Your ability to interpret wafer maps directly influences defect detection and overall production efficiency.

Understanding Die Maps: Key Features

Die maps provide detailed visual representations of individual semiconductor dies on a wafer, highlighting critical metrics such as pass/fail status, yield distribution, and defect locations. These maps utilize color-coding and coordinate grids to pinpoint specific die abnormalities and facilitate root cause analysis during wafer testing and quality control. Unlike wafer maps that show the overall wafer layout, die maps focus on detailed performance and characterization of each die to optimize manufacturing processes.

Visual Representation: Wafer Map vs. Die Map

Wafer maps provide a top-down visual representation of the entire semiconductor wafer, highlighting the spatial distribution of die performance, defects, or yield variations across the wafer surface. Die maps focus on individual die details, offering a close-up view of specific structures, patterns, or test results within a single die. You can use wafer maps to assess overall wafer quality, while die maps enable in-depth analysis at the microscopic die level for process optimization.

Data Granularity: Comparing Information Levels

Wafer maps provide a broad overview of an entire semiconductor wafer, highlighting yield and defect patterns across all dies, while die maps focus on individual die-level data, capturing detailed measurements and test results. The data granularity in wafer maps is coarser, showing spatial trends and cluster defects, whereas die maps offer fine-grained insights into the performance and quality of each specific die. Your analysis benefits from combining both perspectives to optimize yield management and process control effectively.

Common Applications in Semiconductor Manufacturing

Wafer maps visualize the spatial distribution of defects and yield across entire semiconductor wafers, enabling manufacturers to identify pattern-related issues and optimize process steps. Die maps, on the other hand, provide detailed information on individual dies, highlighting pass/fail status and specific defect types within each chip, crucial for quality control and binning processes. Your ability to analyze both map types improves yield enhancement strategies and reduces production costs by pinpointing manufacturing anomalies at different scales.

Workflow Integration: When to Use Each Map

Wafer maps are essential during the early stages of semiconductor manufacturing for visualizing die placement and identifying large-scale wafer defects, while die maps are more focused on individual die inspection and binning during testing and sorting phases. Integrating wafer maps into your workflow helps in assessing wafer-level yield and planning defect rework or retesting strategies. Die maps become crucial after wafer processing to analyze die-specific performance, guiding decisions on packaging and final assembly.

Advantages and Limitations of Wafer and Die Maps

Wafer maps provide a comprehensive overview of the entire wafer, enabling quick identification of patterns in die failure and facilitating yield analysis, yet they may lack detailed insight into individual die characteristics. Die maps offer precise information on each die's condition and performance metrics, optimizing defect localization and process control, but they can be time-consuming to generate and analyze for large volumes. Balancing wafer and die maps leverages the broad spatial context of wafer-level data with the granularity of die-level information, improving semiconductor manufacturing diagnostics.

Impact on Yield Analysis and Defect Detection

Wafer maps provide a spatial representation of defects across the entire wafer, enabling more accurate identification of defect clusters and process variations that affect overall yield. Die maps focus on individual dies, allowing detailed analysis of functional performance and failure modes at the die level, which supports precise defect classification and root cause analysis. Combining wafer and die map data enhances yield analysis by correlating macro-level defect distribution with micro-level die performance, improving defect detection accuracy and process optimization.

Choosing the Right Map for Your Process

Selecting the right map for semiconductor manufacturing hinges on your process requirements and defect analysis goals. Wafer maps offer a comprehensive overview of defect distribution across the entire wafer, ideal for identifying spatial patterns and yield loss areas. Die maps provide detailed, per-die defect information, enabling precise analysis of individual chip performance and process optimization on a micro scale.

Wafer Map vs Die Map Infographic

libmatt.com

libmatt.com